プリント基板設計・シミュレーション・FPGA設計

基板の電磁ノイズを低減したい(EMC対策)

電子機器におけるEMC対策は多岐にわたり、部品による対策やシールドなど様々です。

ただ、製品開発後期におけるEMC対策は、実施できる対策に限りがあったり、対策部品に頼った施策は製品コストの増大につながるため、可能な限り設計上流でEMCの懸念点を抑えておくことが望ましいと考えます。

プリント基板設計によるEMC対策は、『リターン電流経路の確保』や『電源プレーン共振の抑制』など様々な設計手法があり、EMCを理解した熟練の基板設計者によりその品質は担保されます。

課 題

- 製造したプリント基板からノイズが出る。ノイズを低減したい。

最適な

サービス

サービス

プリント基板設計ノウハウやシミュレーション技術を駆使して、最適な分析を行い解決案を提案いたします。

- Step1

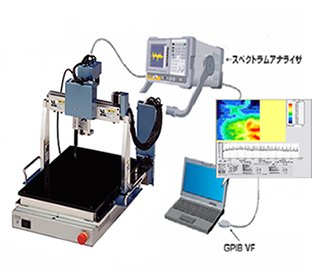

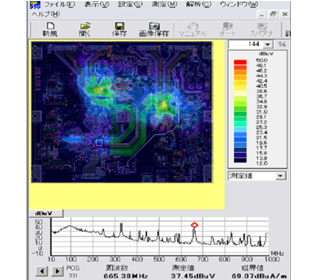

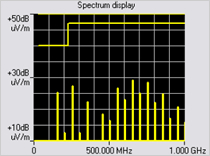

お客様の実機測定データや不具合現象のききとり、あるいは、弊社所有の「ノイズ可視化システム」からノイズ発生の原因を推測いたします。

ノイズ可視化システム

- Step2

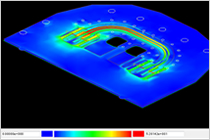

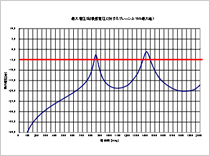

プリント基板データの目視や、プリント基板シミュレーションによる論理的な検証を実施し、ノイズ発生原因を評価してまいります。

プリント基板シミュレーション

- Step3

Step2の評価から最適な対策案を提案いたします。

- Step4

対策案をプリント基板設計に反映し、再びシミュレーションを実施して、対策効果を確認いたします。

- Step5

ノイズ低減の効果が確認された後に、製造に取り掛かります。

その他の課題を見る

関連情報ページへ

関連情報ページへ

EMCシミュレーション

コストや納期などの制約がある中でプリント基板の品質を確保するには、シミュレーションによる検証が大きな助けに。