第1回 Sim技術者のつぶやき 【DDR3のアドレスって配線・終端方法様々ですよね①】

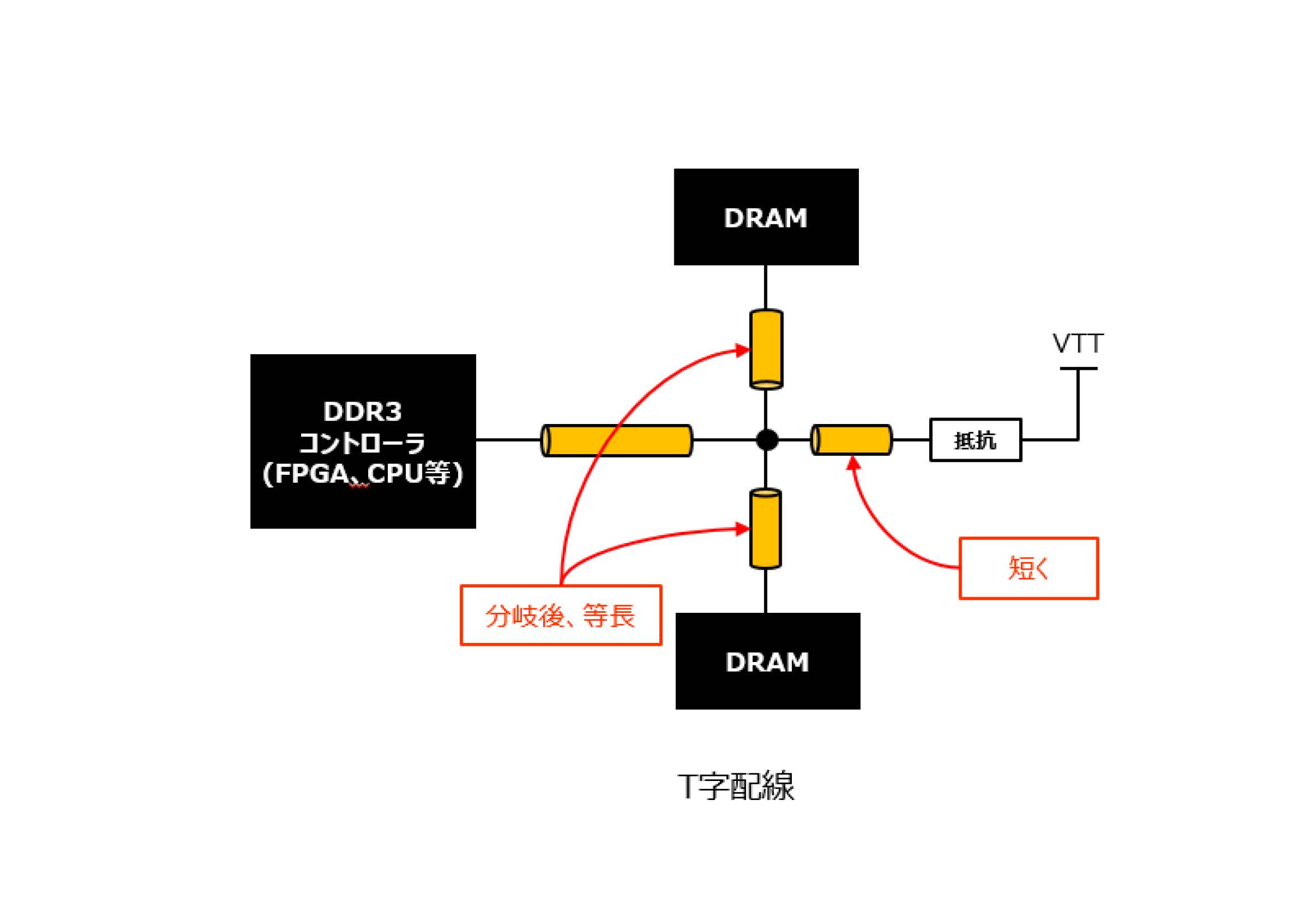

過去DDR2を複数使用した設計品で高機能化に伴ってDDR3へ変更する場合はT字分岐配線をそのまま流用することもありますし、

大きく設計変更を行い、フライバイ配線を選択することもあります。また、ODTが無いのでFPGAやSoCのドライブの強さによってダンピング抵抗、終端抵抗の検討が必要になっていきます。

例えばDRAM近くでT字分岐を行い、分岐後DRAMに行く配線長は等しくなる様にパターンを引きました。

抵抗を追加する場合、幾つか選択肢が取れるかと思います。(下記以外にも対策方法はあります)

①FPGAやSoC近くにダンピング抵抗を追加する

②分岐にプルアップまたはプルダウン終端抵抗を追加する

③分岐後、DRAM近くにダンピング抵抗を追加する

④分岐、DRAM後にプルアップまたはプルダウン終端抵抗を追加する

対策方法は波形の振幅、オーバーシュート、リンギング、スルーレートの状況によって変わります。

振幅が大きければ②や④で分流、オーバーシュートやスルーレートが速ければ①で鈍らせる、反射によるリンギングがある場合は③で分岐のインピーダンス整合を取ることも可能です。

まあ、T字分岐って分岐・分流する背景でFPGAやSoC側のドライブを強くする必要があるから消費電力大きくなりそうですね。