コラム

2023/12/25

第2回 Sim技術者のつぶやき 【DDR3のアドレスって配線・終端方法様々ですよね②】

【DDR3のアドレスって配線・終端方法様々ですよね②】

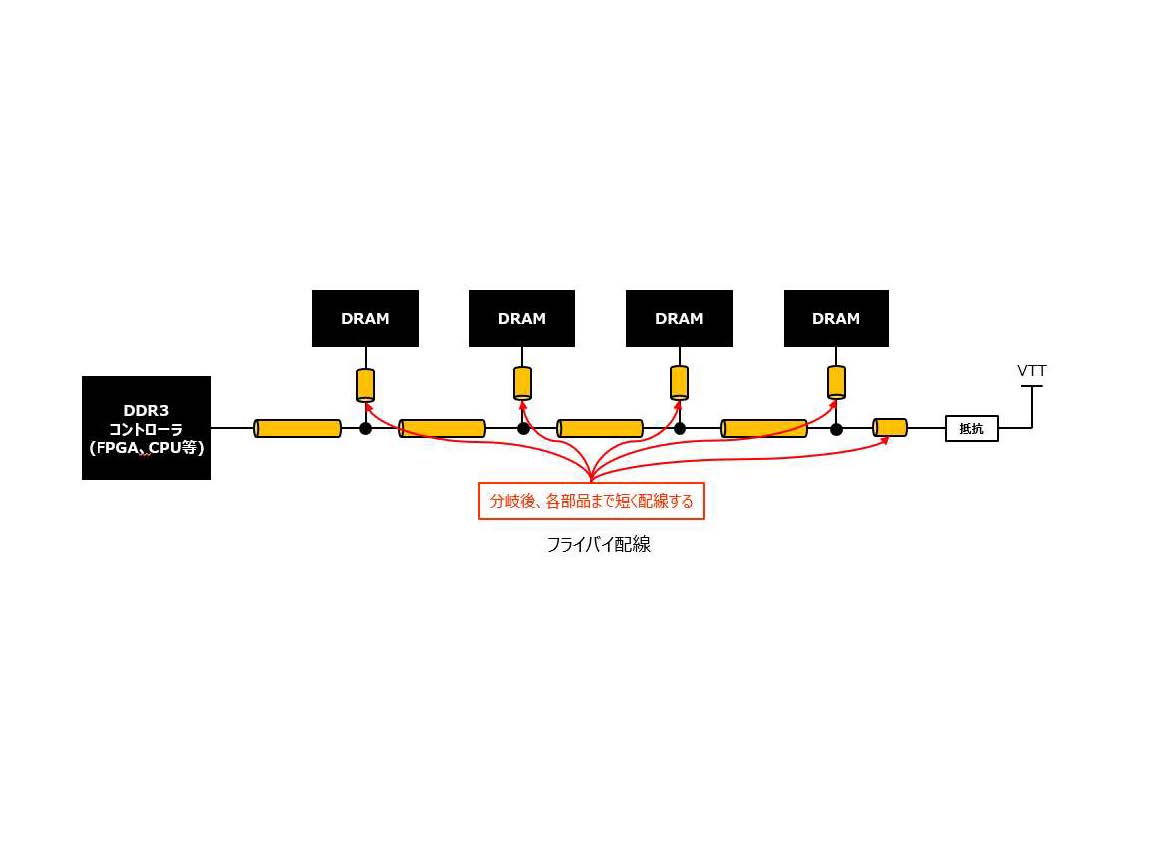

フライバイ配線は複数DRAMを数珠繋ぎで接続した後、VTT電源に終端抵抗で接続することが殆どになるかと思います。この時、ネックになるのは終端抵抗に近いDRAMと遠いDRAMになります。複数DRAMがあると反射によるリンギングで波形が荒れ、どちらかのDRAMがJEDEC規格のVIH(DC)、VIL(DC)がFailすることが多いです。

Failした際にはまず、コントローラのドライブストレングス、VTT終端抵抗の定数調整や最終DRAMからVTT終端までの配置を改善し、波形を確認しますが、それでもJEDECのVIH(DC)、VIL(DC)でNGになる場合があります。そうなると部品追加、配置出来るか検討を行いフライバイ分岐後、DRAM前に抵抗を置いてリンギングを抑えたり、コントローラ近くにキャパシタを置いて波形自体を鈍らせる等の工夫を行って、PASSさせます。

DDR3はコントローラとの兼ね合いもあり、 T分岐配線やフライバイ配線等様々ですが設計やSimのセオリーを抑えて行けば動作します。

フライバイ配線は複数DRAMを数珠繋ぎで接続した後、VTT電源に終端抵抗で接続することが殆どになるかと思います。この時、ネックになるのは終端抵抗に近いDRAMと遠いDRAMになります。複数DRAMがあると反射によるリンギングで波形が荒れ、どちらかのDRAMがJEDEC規格のVIH(DC)、VIL(DC)がFailすることが多いです。

Failした際にはまず、コントローラのドライブストレングス、VTT終端抵抗の定数調整や最終DRAMからVTT終端までの配置を改善し、波形を確認しますが、それでもJEDECのVIH(DC)、VIL(DC)でNGになる場合があります。そうなると部品追加、配置出来るか検討を行いフライバイ分岐後、DRAM前に抵抗を置いてリンギングを抑えたり、コントローラ近くにキャパシタを置いて波形自体を鈍らせる等の工夫を行って、PASSさせます。

DDR3はコントローラとの兼ね合いもあり、 T分岐配線やフライバイ配線等様々ですが設計やSimのセオリーを抑えて行けば動作します。