第3回 Sim技術者のつぶやき 【チップの中とモデル化①】

プリント基板単体に比べてFPGA、SoC等のICデバイスは構造が複雑でシミュレーションする際には構造やモデルの中身を把握しておく必要があります。今回は簡単なBGAパッケージを例としてモデル化を考えてみたいと思います。

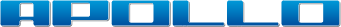

BGAチップで実際に見える部分はチップ外装のケースとはんだボール部(パッケージ基板含む)になります。中身を見てみるとはんだボールからパッケージ基板配線を通してはんだボールの反対面にはダイと直接接続するパッドがあります。ものによってはワイヤボンドを使用してダイとの接続本数を稼いだり、パッケージ基板とダイの間に更にインターポーザ基板を追加してMCM化しているものもあります。

電源理想状態のSIシミュレーションを考えた際にICのモデルはダイの中にあるバッファから、ダイの配線、ワイヤボンド、パッケージ基板の配線、ピン(はんだボール)までとなります。

SIで使用されるIBISモデルでバッファの殆どは[model]キーワードで記述され、パッケージ基板は[Package],[Pin]等RLC形式で記述されるものや最近ではより高速化の対応でTouchstoneのSパラメータモデルとして外に出して使用することがあります。

デバイスベンダから提供されるモデルがどこまでのモデル化を記述しているかをモデルの中身と合わせて確認すると良いかと思います。