プリント基板設計・シミュレーション・FPGA設計

- 2025/09/29

- 社内行事による臨時休業日のお知らせ

- 2025/07/31

- 株式会社ユリ電気商会のグループ参画について

- 2025/06/10

- JPCA2025ご来場のお礼

- 2025/05/22

- JPCA2025出展のお知らせ

- 2025/03/06

- ルネサス「プリファード・パートナー」に認定されました!

- このたび、アポロ技研は ルネサス エレクトロニクスの「プリファード・パートナー」 に認定されました!

プリファード・パートナーとは?

ルネサスと連携し、専門技術を活かした最適なシステムソリューションを提供するパートナー企業です。PoC(概念実証)や設計サービスを通じて、お客様の開発リスクを軽減し、市場投入までの時間短縮を支援します。

当社の対応領域

・ 生産中止部品対策サービス

・ 回路基板開発から量産実装までワンストップ対応

・ 基板シミュレーション / FPGA設計

対応アプリケーション

・ 産業オートメーション・IoTセキュリティ

・ 医療・ヘルスケア・メータ

・ 通信インフラ・HMI・コンピューティング など

対応OS

・ Linux / RTOS / Bare Metal / Android ほか

今後も、ルネサス製品に精通したエンジニアリングサービスを提供し、お客様のものづくりを支えてまいります。

詳細は、お気軽にお問い合わせください!

https://www.renesas.com/ja/support/partners/preferred-partners

- 2025/02/03

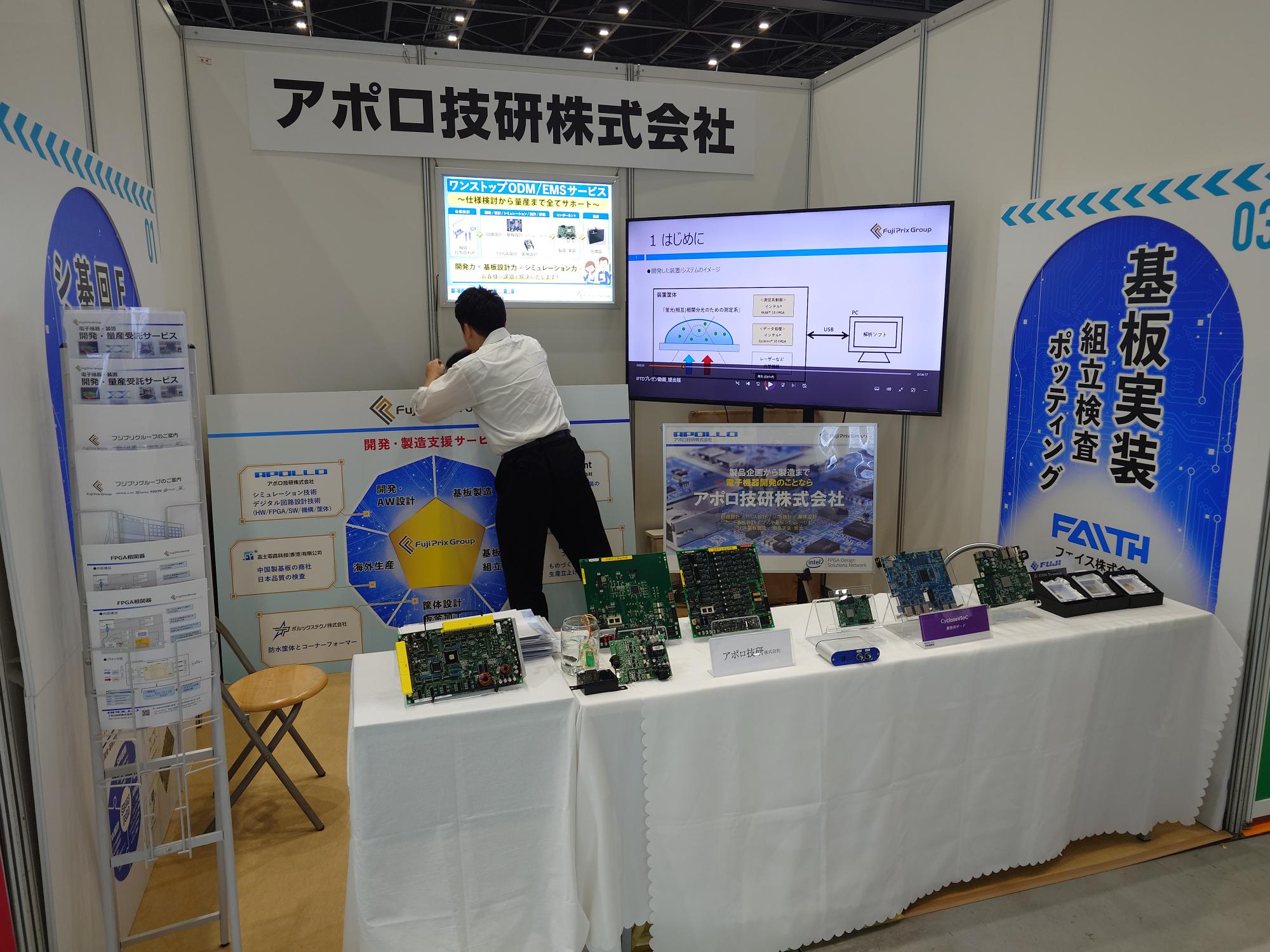

- 「インターネプコンジャパン2025」ご来場のお礼

- 平素は格別のご高配を賜り、厚く御礼申し上げます。 2025年1月22日~24日に行われましたインターネプコンジャパンでは、 お忙しい中、弊社ブースにお立ち寄りいただき誠にありがとうございました。 皆様のおかげをもちまして、盛況のうちに展示会を執り行うことができましたことを心よりお礼申し上げます。 当日、会場でご案内いたしました内容にご不明点などございましたら、弊社担当者へお問い合わせください。 今後とも皆様のご期待に添えますよう、 全力をあげて努める所存でございますので、 何卒、よろしくお願い申し上げます。

- 2025/01/15

- 『インターネプコンジャパン2025』に アポロ技研が出展いたします!1月22日(水)~1月24日(金)開催

- インターネプコンジャパン2025 出展のお知らせ

さて、来る1月22日(水)1月24日(金)インターネプコンジャパン2025にフジプリグループ全体で出展の運びとなりました。

会場では、弊社のFPGA技術の粋を集めた製品をご紹介させていただきます。日時、会場、小間位置・来場事前登録方法

【日時】2025年1月22日(水)~1月24日(金) 10:00~17:00

【会場】東京ビッグサイト 東ホール

【小間位置】E10-31

【来場事前登録方法】

https://www.nepconjapan.jp/tokyo/ja-jp/about/inj.html

<<出展製品>>

製品名:産業用ネットワーク(EtherCAT)のデモシステム(開発中)

皆様のご来場を心よりお待ちしております。

- 2024/12/06

- フジプリグループ「富士プリント工業」シン・試作実装ラインのご案内

- 富士プリント工業のシン・試作実装ラインをご紹介

設計から実装まで開発期間を短縮いたします。

最少:1台から生産対応

最短:部品集約から1営業日で完成

EMSトータルソリューションを提供

開発設計から実装完成まで社内完結

迅速なサービスで開発期間の短縮を提供します

1. 高速チップマウンター

2. N2リフロー炉

3. 局所半田付装置

相模原工場 実装対応スペック

使用半田: 無鉛

対応基板サイズ: Min: 70×50mm / Max: 500×370mm

対応部品:SMD: 極小チップ0603~、BGA LGA実装対応

高さMAX27mmまでリフロー実装可能

DIP: 局所はんだ付け共通適用

部品形態:リール / トレイ / バラ(実装数・形態により要相談)

[会社情報]

アポロ技研株式会社

本社: 〒224-0037 神奈川県横浜市都筑区茅ヶ崎南二丁目6番25号

TEL: 045-949-0700 / FAX: 045-949-0704

メール: AP-info_hp@fujiprix.co.jp

Web: https://www.apollo-g.co.jp/

- 2024/12/06

- 『Edge Tech+2024』ご来場のお礼

- 『Edge Tech+2024』ご来場のお礼

2024年11月20日(水)~22日(金)に行われましたEdge Tech+2024では、 お忙しい中、弊社ブースにお立ち寄りいただき誠にありがとうございました。

皆様のおかげをもちまして、盛況のうちに展示会を執り行うことができましたことを心よりお礼申し上げます。

当日、会場でご案内いたしました内容にご不明点などございましたら、弊社担当者へお問い合わせください。 今後とも皆様のご期待に添えますよう、 全力をあげて努める所存でございますので、 何卒、よろしくお願い申し上げます。

- 2024/11/07

- 『Edge Tech+ 2024』に アポロ技研が出展いたします!11月20日(水)~11月22日(金)開催

- Ede Tech 出展のお知らせ

さて、来る11月20日(水)~22日(金)にEdge Techに出展の運びとなりました。

会場では、弊社のFPGA技術の粋を集めた製品をご紹介せていただきます。日時、会場、小間位置・来場事前登録方法

【日時】2023年11月20日(水)~11月22日(金) 10:00~17:00

(21日(木)のみ18:00まで)

【会場】パシフィコ横浜(展示ホールA・B・C/アネックスホール)

【小間位置】BA-09

【来場事前登録方法】https://www.jasa.or.jp/expo/

<<出展製品>>

製品名:Altera® 最新製品Agilex™ 5 FPGA & SoC FPGAデモボード(開発中)

製品名:産業用ネットワーク(EtherCAT)のデモシステム(開発中)

皆様のご来場を心よりお待ちしております。

======================================================

エッジテクノロジーに新たなプラスで加速するDXと事業変革

アポロ技研は、”開発力”×”基板設計力”×”シミュレーション力”でお客様の課題を解決いたします。

アポロ技研の強みはHW・FPGA設計者、AW設計者、SIM技術者が一体となり、PI/SI/EMCシミュレーションの有効活用により品質の良い基板設計、物づくりを実現することです。インターフェースやデバイスが高速化することでシミュレーションの活用は不可欠となっており新しい技術の取得が欠かせません。弊社はDDR5など新しい技術を取得し高い技術でシミュレーションを行い品質の高い設計を提供いたします。上流工程~ものづくりまで携わっているアポロ技研におまかせください。

- 2024/11/04

- 『名古屋 ネプコン ジャパン』ご来場のお礼

- 『名古屋 ネプコン ジャパン』ご来場のお礼

2024年10月23日~25日に行われましたネプコンジャパンでは、 お忙しい中、弊社ブースにお立ち寄りいただき誠にありがとうございました。

皆様のおかげをもちまして、盛況のうちに展示会を執り行うことができましたことを心よりお礼申し上げます。

当日、会場でご案内いたしました内容にご不明点などございましたら、弊社担当者へお問い合わせください。 今後とも皆様のご期待に添えますよう、 全力をあげて努める所存でございますので、 何卒、よろしくお願い申し上げます。

- 2024/10/03

- 『名古屋 ネプコン ジャパン』10月23日(水)~10月25日(金)にアポロ技研が出展します

- 【名古屋】 ネプコンジャパン 出展のお知らせ

平素は格別のご高配を賜り、厚く御礼申し上げます。

さて、来る10月23日(水)~25日(金)に「【名古屋】 ネプコンジャパンに出展の運びとなりました。

会場では、弊社のFPGA技術の粋を集めた製品をご紹介せていただきます。

≪展示会概要≫

出展展示会:【名古屋】ネプコンジャパン

ネプコンジャパン(主催 RX Japan(株)

日時:2024年10月23日(水)~25日(金)10:00~17:00

場所:ポートメッセなごや第1展示館(交通アクセス:https://portmesse.com/access)

小間番号:N15-39

≪出展製品≫

製品名:インテル® Cyclone®V SOCを搭載FPGAボード

産業機器を対象とした画像処理ボード FPGA相関器ボード(量産中)

皆様のご来場を心よりお待ちしております。

イベント参加登録はこちら>

来場登録(入場用バッジ登録フォーム)2024年10月名古屋開催 (nepconjapan.jp)

================================================

- 2024/09/18

- フジプリ通信を更新しました!【5dayインターンシップ】

- フジプリグループ採用サイト内の「フジプリ通信」を更新しました。 今回は新たにインターンシップの記事を掲載しました。 https://recruit.fujiprix.com/media/category02/a17 今後も社内イベントや採用活動について掲載していく予定ですので、 是非ご覧ください!

- 2024/05/17

- フジプリ通信「2024年度新入社員研修」の記事を更新しました!

- フジプリグループ採用サイト内の「フジプリ通信」を更新しました。 今回は新入社員研修についての記事を掲載しました。 https://recruit.fujiprix.com/media/category01/a16 ・記事タイトル:2024年度新入社員研修 今後も社内イベントや採用活動について掲載していく予定ですので、 是非ご覧ください!

- 2024/04/18

- 採用サイトの「フジプリ通信」を更新しました!

- フジプリグループ採用サイト内の「フジプリ通信」を更新しました。 今回は入社式についての記事を掲載しました。 https://recruit.fujiprix.com/media/ ・記事タイトル:2024年度入社式を行いました! 今後も社内イベントや採用活動について掲載していく予定ですので、 是非ご覧ください!

- 2024/01/29

- 【プリント配線板 EXPO】に アポロ技研が出展いたしました![2024年1月24日(水)~26日(金)10:00~17:00開催]

日時、会場、小間位置・来場事前登録方法

【日時】2024年1月24日(水)~26日(金)10:00~17:00

【会場】東京ビッグサイト East ホール(交通アクセス:https://www.bigsight.jp/visitor/access/)

【小間位置】CR-14

【来場事前登録方法】今回から紙の招待状を配布ではなく、事前登録制となります。事前登録は下記URLよりお願いします。

https://www.nepconjapan.jp/tokyo/ja-jp/register.html?code=0915904596570813-LDH

======================================================

≪出展製品≫

製品名:FPGA相関器ボード(量産中)

概要: FPGAの光学分野への応用 FCCS法(蛍光相関)搭載分析装置の中の基板 等。

- 2023/10/11

- 『インテル® FPGA テクノロジー・デイ(IFTD) 2023』 11月21日(火)よりオンライン開催!11月22日(水)にアポロ技研が発表いたします。

産業、放送、医療、防衛、ネットワーク、データセンター、車載、AI (人工知能)、

IoT など、幅広い分野において FPGA (フィールド・プログラマブル・ゲート・アレイ) の採用は拡大の一途にあります。

インテルの FPGA テクノロジーおよび関連製品の最新情報、パートナー各社様の

ソリューションなどを一挙に紹介するオンラインイベント

「インテル® FPGA テクノロジー・デイ 2023 ( IFTD ) 」 を今年も開催します。

11月に公開されるイベントサイトではパートナー各社様のソリューション資料などをまとめてダウンロードも可能です。

ぜひ、ご登録ください。

================================================

会 期:2023年11月21日 (火) 、11月22日 (水)、11月24日(金)

開催方法:オンラインイベント

プログラム(仮):基調講演|インテル講演|協賛企業講演|デモ動画|

各社資料のダウンロード

対 象 者:・チーフ・テクノロジー・オフィサー (CTO)

・システムプランナー

・ハードウェア・エンジニアおよびマネージャー

・PCB 設計者

・ソフトウェア・エンジニアおよびマネージャー

・アルゴリズム・デベロッパー

・プロダクト・マネージャー

参 加 費:無料 (事前登録制)

主 催:インテル株式会社

=================================================

- 2023/10/06

- 『Edge Tech+ 2023』に アポロ技研が出展いたします!11月15日(水)~11月17日(金)開催

日時、会場、小間位置・来場事前登録方法

【日時】2023年11月15日(水)~11月17日(金) 10:00~17:00

(16日(木)のみ18:00まで)

【会場】パシフィコ横浜(展示ホールA・B・C/アネックスホール)

【小間位置】CR-14

【来場事前登録方法】https://www.jasa.or.jp/expo/

======================================================

エッジテクノロジーに新たなプラスで加速するDXと事業変革

アポロ技研は、”開発力”×”基板設計力”×”シミュレーション力”でお客様の課題を解決いたします。

アポロ技研の強みはHW・FPGA設計者、AW設計者、SIM技術者が一体となり、PI/SI/EMCシミュレーションの有効活用により品質の良い基板設計、物づくりを実現することです。

インターフェースやデバイスが高速化することでシミュレーションの活用は不可欠となっており新しい技術の取得が欠かせません。

弊社はDDR5など新しい技術を取得し高い技術でシミュレーションを行い品質の高い設計を提供いたします。

- 2023/05/10

- JPCA Show 2023出展のご案内

- 2023/02/16

- 採用サイト内の「フジプリ通信」を更新しました!

- フジプリグループ採用サイト内の「フジプリ通信」を更新しました。

今回は新たに以下3つの記事を掲載しました。

https://recruit.fujiprix.com/media/

・【アポロ技研】理系学生向けイベントに参加しました!

・グループ合同の研修を行いました!「次世代リーダー研修」第2回

・【アポロ技研】インターンシップ開催!!

今後も社内イベントや採用活動について掲載していく予定ですので、

是非ご覧ください!

- 2022/06/03

- 日本経済新聞に掲載されました!

- 卓上装置開発「空気壁でコロナ遮断」

当社が研究開発に携わりました卓上装置の開発についての記事が、日本経済新聞

(6月3日の朝刊15面<テック>)に掲載されました。

当案件は、名古屋大学様との共同開発で、当社は不活性化装置とエアカーテンの構造部分の

機構設計と製造を担当させていただきました。

<弊社担当者コメント>

・3Dプリンターを使用することを提案し、低コストを実現しています。

・エアカーテンの風量調整を直に行いたいというユーザーの希望を踏まえ、当初から決まっていたエアカーテンのデザインを壊さないように、風量調整をするための構造を考えて提案し、完成させています。

- 2021/04/26

- 世界初のエレクトロニクス3Dプリンター FPM-Trinity

- 協業PRページ のお知らせ

弊社の協業メーカーである㈱FUJIの

「世界初のエレクトロニクス3Dプリンター FPM-Trinity」についてのPRページを作成しています。

<PRページ>http://www.apollo-g.co.jp/task/fpm_trinity/

FPM-Trinityは、基板製造・部品実装・樹脂成型の3つの工程1台で実現します。

従来の電子基板の枠にとらわれず、3Dプリンターの特性を活かし自由に形状をカスタマイズでき、 工程間の移動時間が削減できるので納期の短縮を可能にします。

サンプルの受託製造が大好評です。ぜひサンプル試作にご活用ください。

- 2021/04/22

- AdaptEco車載端末(AD-E1)に関する重要なご報告

- お客様各位

AdaptEco 車載端末(AD-E1) に関する重要なご報告

平素より格別のご愛好を賜り誠にありがとうございます。

この度は現在お使い頂いているAdaptEco車載端末に関する販売終了ならびにサポート終了に

関するご案内となります。

製品で使用しているGPS受信機「CCA-552J」の耐用年限が2024/9/1迄となっており、それ

以降はすべてのAdaptEcoが使用できなくなる事が判明いたしました。

また、製品開発を行った際に最新だったWindowsXPもOSがアップデートされ、現在の

Windows10でのソフトウェア開発についても製品の供給が困難のため断念いたしました。

長きにわたりご愛用を頂き大変心苦しい決断ではございますが、製品の販売を終了させて

いただく事をご了承くださいますようお願いを申し上げます。

なお、サポート(不具合診断や電池、コネクタの交換)については、電池とコネクタの在庫が

無くなるまでの対応とさせていただきます。

ご不便をおかけいたしますこと深くお詫び申し上げます。

ご了承賜りますよう心よりお願い申し上げます。

アポロ技研株式会社

- 2021/01/25

- アポロ技研Webセミナー のお知らせ

- ・タイトル

LPDDR4動作不具合基板から学ぶグランド設計の重要性

・概要

本セミナーでは、あるお客様よりご相談いただいた、

LPDDR4動作不具合基板に対しシミュレーションを活用して

問題解決に向かった事例を通じてグランド設計の重要性を

ご紹介させて頂きます。

・掲載期間

1月25日(月)~2月1日(月)

・視聴方法

下記URLから弊社のHPにアクセスしていただき、簡単な登録をして頂くと視聴ができます。

<登録用URL>

http://www.apollo-g.co.jp/online_seminar/

録画でのセミナーなので、お好きな時間に視聴できます。

掲載期間にはご注意下さい。

――――――――――――――――――――――――――――――――――――――――――

シミュレーションに関するご相談などございましたら下記までお気軽にお問合せ下さい。

お待ちしております。

Tell:045-949-0700

Mail:info0609@apollo-g.co.jp

- 2020/10/29

- 当社における新型コロナウイルス感染者の発生について

-

各位

2020年10月29日

アポロ技研株式会社

当社における新型コロナウイルス感染者の発生について

10月26日 および 10月27日 に当社従業員2名が新型コロナウイルスに感染していることが

判明いたしました。

1名は 10月21日まで勤務し帰宅後、発熱・倦怠感の症状あり一度は風邪との診断でしたが

症状の改善が見えず、PCR検査の結果 10月27日に感染が判明し、現在は保健所の指示にて

自宅療養中です。

もう1名は 10月23日 まで勤務しており、同じく帰宅後、発熱・倦怠感の症状あり

10月26日にPCR検査を受け感染が判明、現在は医療機関にて隔離療養中です。

濃厚接触者は5名で、保健所の指導のもとPCR検査の実施および自宅待機のうえ経過観察を

行っています。

共有していたスペースにつきましては、既に消毒作業を実施し業務を再開しております。

関係者の皆様には多大なご心配をおかけしておりますが、当社は保健所を含む関係各所と

連携のうえ、今後もお客様、お取引様、従業員とその家族の安全確保と感染拡大の防止

を最優先に考え、事業の継続に努めてまいります。

以上

- 2020/10/16

- Keysight Design Forum 2020 オンラインセミナーのお礼。

- この度は、お忙しい中、弊社の要素技術担当者が講演するオンラインセミナー

「高速信号伝送におけるグランド設計の重要性」にご登録・ご視聴いただき、

誠にありがとうございました。

おかげさまで全セッションの中で最多の登録数、視聴数をいただけました。

登録者数:500名弱

なお、当セミナーについては弊社ホームページでも視聴できるよう検討中です。

今後ともどうぞ宜しくお願い申し上げます。

- 2020/09/15

- Keysight Design Forum 2020

- オンラインセミナーにて弊社技術担当者が、 「高速信号伝送におけるグランド設計の重要性」 と題して講演をさせていただくこととなりました。 詳細はこちらから

- 2020/07/13

- 四会富仕電子有限公司上場のお知らせ

- 富士プリント工業株式会社(並びに富士電路科技(香港)有限公司)の永久パートナーである

四会富仕電子有限公司が、この度中国深圳証券市場(創業板)に上場しましたのでお知らせ

します。

四会富仕電子科技股份有限公司(設立当時は四会富士)の董事長、劉天明と

富士プリント工業株式会社の会長、荒井眞澄は、2008年の創業準備から今日まで

パートナーとして深く経営に関わってきました。

今後も両社の関係は永久パートナーとして、更なる関係強化に努め連携を図り、

お客様に貢献できる企業を目指してまいります。

2020年7月13日中国深圳証券(創業板)市場

証券番号:300852

2020年7月13日

- 2020/07/03

- 技術情報協会 書籍発刊について

- 弊社、要素技術推進部 遠藤が執筆した記事が下記書籍に掲載され、5/29に発刊されました。

書籍名:【プリント配線板材料の開発と実装技術】(発刊元:株式会社技術情報協会)

内容(タイトル):「高速メモリ設計に向けたシミュレーション技術と動作不具合対策」

https://gijutu.co.jp/doc/b_2054.htm

- 2020/04/10

- 新型コロナウイルスに対する当社の対応について

- 2020年4月10日

アポロ技研株式会社

アポロ技研株式会社は、新型コロナウイルス感染症(COVID-19)に対しまして、以下の通り対応しております。

●お客様、お取引先様、グループ従業員とその家族、地域社会の安全を最優先とします。

●部門によりテレワーク制度を推進しています。

●web会議の積極的な活用を推進しています。

●マスク着用、咳エチケット、手洗い、消毒、体温測定の実施を徹底しています。

●従業員に発熱などの症状が見られる場合は、自宅待機とし、保健所等の指示に従います。

●パンデミックウィルススクリーニング質問を実施しています。

●不要不急の国内外出張を原則禁止としています。

●多人数が参加するイベントやセミナーへの参加を禁止しています。

●10名以上の社内会議を禁止しています。

当社は通常稼働していますが、今後の状況により必要な対応を速やかに取ってまいります。

- 2019/12/23

- 『インターネプコンジャパン』に出展します(1月15日~)

- 『インターネプコンジャパン』にフジプリグループ全体で出展致します。

グループだからできる ”ワンストップオーダー”

ぜひ当社ブースへお立ち寄りください。

◆会期:2020年1月15日(水)~17日(金)

10:00~18:00(最終日のみ17時まで)

◆会場:東京ビッグサイト

弊社ブース 西2ホール W5-43

- 2019/10/15

- 台風19号による被害を受けられた皆様へ

- この度の台風19号により被災された皆様、ならびにそのご家族の皆様に心よりお見舞い申し上げます。 皆様の安全と被災地域の一日も早い復興を心よりお祈り申し上げます。

- 2019/09/19

- 11月8日(金)《Asian IBIS Summit & 第8回 JEITA IBISセミナー》開催

- 11月8日(金)に「IBIS Summit&IBISセミナー」が開催されます。

当社の要素技術担当者が委員として運営に携わっております。(講演は未定)

----------------------------------------------------------------------------------------

【日時】2019年11月8日(金)

【会場】秋葉原UDX 4F NEXT1 東京都千代田区外神田4丁目14-1

■第8回JEITA/IBISセミナー 10:00スタート 9:30受付開始

<テーマ>IBIS What's New!!(IBIS Ver5.0~Ver7.0の最新情報)

■Asian IBIS Summit(TOKYO)13:00スタート

<テーマ>IBISモデルに関する開発状況、今後の展望・課題、事例紹介等

【受講料】無料

【お申込方法】お申し込み方法および詳細はJEITA ECセンターのホームページからお願い致します。

http://ec.jeita.or.jp/jp/modules/eguide/event.php?eid=41

-----------------------------------------------------------------------------------------

- 2019/09/11

- Keysight Design Forum 2019 出展 (10月18日)

- 10月18日(金)開催のキーサイトデザインフォーラム2019に弊社が出展いたします。

また、セミナーにて弊社技術担当者が、

「低コスト化への挑戦~LPDD4基板設計事例~」

と題して講演させていただくこととなりました。(11:15~11:55)

ご来場お待ちしております。

<開催概要>

日時:2019年10月18日(金) 9:50 ~ 17:00 (9:20 受付開始)

セミナー終了後に、Beer Party を開催します。

会場:御茶ノ水ソラシティ カンファレンスセンター

住所:〒101-0062 東京都千代田区神田駿河台4-6

交通:JR中央・総武線 御茶ノ水駅 聖橋口 徒歩1 分

東京メトロ 千代田線 新御茶ノ水駅B2 出口 直結

東京メトロ 丸ノ内線 御茶ノ水駅 出口1 徒歩4 分

都営地下鉄 新宿線 小川町駅 B3 出口 徒歩6 分

会場アクセス:https://solacity.jp/cc/access/

参加費:無料(事前登録制)

申込締切:定員になり次第締め切り

- 2019/06/14

- 『JPCAshow2019』へのご来場ありがとうございました

- 2019年6月5日~6月7日に開催されました「JPCAshow2019」において、

当社のブースへご来場いただいた大変多くの皆様にお礼申し上げます。 来場していただいたお客様からは、当社のPI,SIシミュレーションや、IOTに

関するご相談等をいただきました。

各種業務単体でも、回路設計から基板設計・製造・実装・筐体含め製品化まで、

一貫してのご相談でもお手伝いさせていただきますので、ぜひお声かけください。

今後とも宜しくお願い申し上げます。

- 2019/05/17

- 日本科学未来館メディアラボ第21期展示「ぴったりファクトリ」公開

- 関西学院大学とアポロ技研(株)が共同研究開発しております「触感計測装置」が、日本科学未来館にて紹介されておりますのでお知らせいたします。

※日本科学未来館「ぴったりファクトリ」展示会

◎ゾーン2.「ぴったり」をさぐる

【触覚をデータ化する「触感定量化」実験イメージ】の装置

この触感計測装置は、触った感覚(触感)をデジタルデータ化する装置です。

関西学院大学とアポロ技研が共同で開発・設計・製造しております。

弊社の回路設計から筐体設計まで一貫して行える体制により、共同研究による触感

計測装置を作ることができました。

是非ご来場いただき、ご見学・ご体感下さい!!

-------------------------------------------------------------------------------------------------

■開催概要

名称: メディアラボ第21 期展示 「ぴったりファクトリ」

会期: 2019 年5 月16 日(木)~9 月1 日(日)

時間: 午前10 時~午後5 時(入館券の購入は閉館時間の30 分前まで)

場所: 日本科学未来館 3 階 常設展「メディアラボ」

東京都江東区青海2-3-6

入館料: 大人620 円、18 歳以下210 円

休館日: 毎週火曜日(ただし、7/23・30、 8/6・13・20・27 は開館)

出展者: 国立研究開発法人科学技術振興機構

センター・オブ・イノベーション(COI)プログラム

「感性とデジタル製造を直結し、生活者の創造性を拡張するファブ地球社会

創造拠点」

長田典子(関西学院大学 教授)、田中浩也(慶應義塾大学 教授)

主催: 日本科学未来館

(日本科学未来館HP:メディアラボ第21期展示「ぴったりファクトリ」公開)

https://www.miraikan.jst.go.jp/info/1904181124165.html

-------------------------------------------------------------------------------------------------

- 2018/10/26

- Asian IBIS Summit & 第7回JEITA_IBISセミナー

- ■IBISセミナー

<テーマ>IBISとS-parameter

10:00スタート

■Asian IBIS Summit(TOKYO)

13:00スタート

<テーマ>IBISモデルに関する開発状況、今後の展望・課題、事例紹介等

開催情報

【日時】

2018年11月12日(月)

10:00~16:45(9:30受付開始)

【会場】

東京都千代田区外神田4丁目14-1 秋葉原UDX 4F NEXT1

【受講料】

無料

【お申込方法】

お申し込み方法および詳細はJEITA ECセンターのホームページからお願い致します。

http://ec.jeita.or.jp/jp/modules/eguide/event.php?eid=40

- 2018/10/05

- Keysight Design Forum 2018 に出展します!

- 10月16日(火)にキーサイトデザインフォーラム2018に弊社が出展いたします。

セミナーにて弊社の技術担当者が、

「LPDDR4 の概要とプリント基板設計、シミュレーション事例」

と題して講演をさせていただくこととなりました。 (13:50 - 14:30)

---------------------------------------------------------------------------------------------

日時2018 年10 月16 日( 火) 9:50 ~ 17:00 (9:20 受付開始)

セミナー終了後に、Beer Party を開催します。

会場御茶ノ水ソラシティ カンファレンスセンター

住所:〒101-0062 東京都千代田区神田駿河台4-6

交通:JR 中央・総武線 御茶ノ水駅 聖橋口 徒歩1 分

東京メトロ 千代田線 新御茶ノ水駅B2 出口 直結

東京メトロ 丸ノ内線 御茶ノ水駅 出口1 徒歩4 分

都営地下鉄 新宿線 小川町駅 B3 出口 徒歩6 分

会場アクセス: https://solacity.jp/cc/access/

参加費無料(事前登録制)

- 2018/09/14

- 「インテル® FPGAテクノロジー・デイ2018」 に出展します

- 「インテル® FPGAテクノロジー・デイ2018」 に出展パートナーとして参加します!

<開催概要>

日時:2018年9月21日(金)

会場:ホテル雅叙園東京

参加費:無料 (事前登録制) ※お名刺を2枚ご持参ください。

対象:チーフ・テクノロジー・オフィサー (CTO)

システムプランナー

ハードウェア・エンジニアおよびマネージャー

PCB 設計者

ソフトウェア・エンジニアおよびマネージャー

アルゴリズム・デベロッパー

プロダクト・マネージャー

インテル®Arria® 10 FPGA を使用した高速インタフェース(JESD204B企画)制御のデモンストレーションを紹介します。

詳細はこちらになります。

https://www.intel.co.jp/content/www/jp/ja/events/fpga/overview.html

- 2017/10/27

- 大阪支店移転のお知らせ

- 平素は格別のご高配を賜り厚く御礼申し上げます。

さて、このたびアポロ技研株式会社 大阪支店と、富士プリント工業株式会社 大阪営業所は、平成29年11月1日より、 新事務所に統合移転することになりました。

これに伴い、大阪支店から大阪営業所に呼び方を変更いたします。

これを機に社員一同気持ちを新たにし、皆様のご信頼にお応えできるよう倍旧の努力をしてまいる所存でございます。

今後とも一層のお引き立てを賜りますようお願い申し上げます。

事務所移転日: 平成29年11月1日(水)

新住所: 〒541-0041

大阪府大阪市中央区北浜3丁目2番23号 大阪信愛ビル2階12号室

新電話番号 : 平成29年11月6日(月)より変更

アポロ技研(株) TEL:06-4256-4658 FAX:06-4256-4676

富士プリント工業(株) TEL:06-4256-4668 FAX:06-4256-4676

○ 電車でお越しの方

淀屋橋駅(京阪本線)地下道16番出口(当ビル地下2階)よりエレベーターにて直通

○ お車でお越しの方

名神阪高速道路 豊中IC(JCT)より 阪神高速11号池田線

→阪神高速1号環状線→都市高北浜 北浜出口で下車6分

- 2017/02/01

- フジプリグループの一員となりました

- この度、アポロ技研株式会社は平成28年12月17日付にて、フジプリグループ株式会社 が全株式を取得しグループの一員として、事業を執り行うことになりました。 今般のグループ化により弊社の回路・基板設計・シミュレーション分野のノウハウとフジプリグループのノウハウを融合し、これまで以上のサービス向上ができるものと確信しております。今後はグループの総力を結集しシナジー効果を最大限に発揮して、さらなるサービスの向上と発展を期し、皆様にご満足いただけますよう全力を尽くす所存でございます。 何卒、従来にも増してご指導お引き立てを賜りますようお願い申し上げます。

- 2016/08/26

- 会社案内のデータを公開しました

- 公開資料ページ にて弊社会社案内のデータを公開しました。是非ご覧ください!

- 2016/03/18

- ホームページをリニューアルしました

- 今後とも変わらぬご愛顧のほどよろしくお願い申し上げます。

- 2015/09/15

- アルテラパートナーブースに出展いたします。

- 2015年9月15日 今回、11/18(水)~11/20(金)に開催されるET2015のアルテラパートナーブースに出展いたします。

- 2014/04/17

- アルテラコーポレーションとDSN契約を締結しました

- 2013年4月 アルテラコーポレーションとDSN契約を締結しました。 アルテラ社の各種FPGA、IPを使用した通信・映像・高速シリアル・工業製品等の RTL設計および高品質な基板設計を含めたトータル・ソリューションを提供します。

ニュースリリース